【产业链系列文章】芯片产业链上市公司盘点之EDA软件与IP核篇【产业链系列文章】芯片产业链上市公司盘点之EDA软件与IP核篇

日期:

2022-01-27

导语:在《芯片产业链上市公司盘点之IC设计篇》中,我们为大家介绍了芯片在设计环节的流程和厂商。芯片设计可大致分为规格制定、逻辑合成和电路布局三个环节,如果把芯片比作一座大厦的话,IC设计的产出就是大厦的设计图纸,EDA软件就是绘制这张图纸的操作工具,只不过相比于建筑设计,IC设计的复杂度要高得多。

芯片的设计涉及功能、算法、协议等等,利用EDA软件工具,IC设计工程师们能够实现从功能模块拆解、电路设计、性能分析到输出IC版图或PCB版图的整个过程。一颗芯片上有数亿到十亿以上的晶体管,设计的过程要持续模拟和验证,有了EDA软件,芯片设计工作的效率可以大大提高。同时,EDA软件工具在芯片制造和封测环节也有应用。IP核是芯片上具有较为独立的功能模块的成熟设计,可编辑,可复用,IC设计环节通常会评估整体设计成本来进行IP的外采。IP核的模式进一步提高了IC设计过程的整体效率。

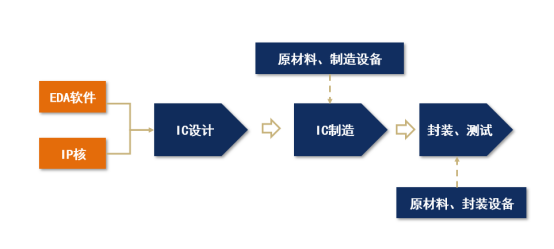

一、EDA软件与IP核在全产业链中所处位置

半导体产业链可大致分为设计、晶圆制造与封装测试三大环节,芯片设计环节产出各类芯片的设计版图,晶圆制造环节根据设计版图进行掩膜制作,形成模版,并在晶圆上进行加工,封装测试环节对生产出来的合格晶圆进行切割、焊线、塑封,并对封装完成的芯片进行性能测试。

在芯片设计的过程中,EDA软件与IP核已成为广泛使用的必备工具。EDA是 Electronic Design Automation的简称,即电子设计自动化。运用EDA 设计方式形成的工具我们称为EDA软件。EDA软件使得作图环节自动化并对设计完成的电路图进行实时模拟与仿真分析,将设计师从繁琐的画图作业中解放出来,专注于理解芯片功能需求与进行逻辑设计;仿真分析使得芯片在设计阶段尽可能实现贴近实际物理效果的验证,降低设计企业流片试产失败的风险,减少不必要的重复工作与费用支出。

IP核指芯片设计中预先设计完成并经过验证的标准化功能模块,通过使用IP核,设计人员无需从0开始对所有细节进行重新设计,而是借助特定的IP核经调整后快速完成某个模块的设计,大幅降低了芯片设计周期与设计难度。

集成电路发展早期,产品结构简单,设计师可通过手动作图满足设计要求。摩尔定律在现实中不断得到验证,单位面积晶圆集成的晶体管数量不断上升,作图量与难度猛增推动设计工具的不断发展。20世纪70年代可编程逻辑技术出现,开发人员开始了将设计流程自动化的尝试,硬件描述语言VHDL与Verilog随之产生,开发人员使用硬件描述语言完成对设计逻辑的描述后将代码输入电子设计自动化软件中即可自动生成电路图,EDA软件开始出现并商业化。

随着集成电路设计的不断发展,EDA软件不仅能够在设计环节辅助开发者进行设计,亦能够对设计完成的电路图进行仿真分析,模拟电路制成后的实际运作,使开发者能够在试产前尽可能发现错漏,从而实现电路的优化设计。芯片设计完成后的试产环节(流片)意义重大,流片失败意味着返工重新进行设计与再一次支付高昂的流片费用。EDA软件也在制造环节中得到应用,晶圆制造商通过EDA软件对自身的产品进行建模并将模型发送至各芯片设计企业,使芯片设计企业能够将代工厂商的技术工艺特点考虑到设计中,加强了芯片产业链上下游的协同。在EDA软件迅速发展的同时,芯片设计的另一重要工具IP核也得到了广泛应用。随着集成电路功能复杂化与产品推新周期缩短的趋势显现,半导体领域出现独立IP厂商,独立IP厂商为芯片设计企业直接提供经过验证的IP模块库,设计企业的开发者无需从头设计,而是直接调用特定功能模块,经过调整后便可实现所需功能,芯片设计企业可将其余人力物力倾斜于产品定义、系统架构、市场营销等环节。

为了更好地理解IP核的逻辑,我们可将IP核类比为汽车生产过程的动力系统、转向系统、悬架系统、车身系统等部分,主机厂并不进行所有汽车零部件的生产,而是将大部分零部件外包给一级与二级供应商,自身则专注于动力系统与组装技术的研发,并在生产过程中将汽车的所有零部件进行协同优化与系统集成。IP模块库的使用极大降低了设计的难度与时间周期,芯片设计由电路设计转变为系统设计。

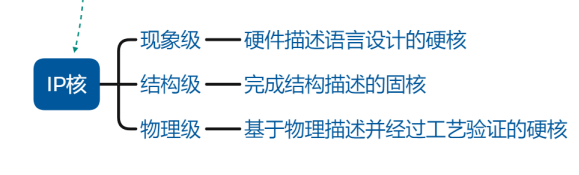

按开发程度进行分类,IP核的分类如下图所示,开发程度越高的IP核,后期可编辑程度越低,而可预见性更高。

二、EDA软件、IP核主要上市公司汇总

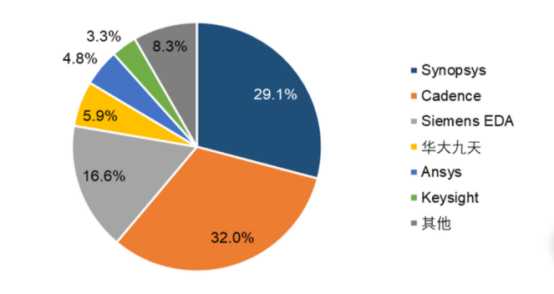

EDA与IP核行业均为集中度极高的寡头垄断市场,根据赛迪智库2020年统计数据,国际三巨头Synopsys、cadence与西门子旗下子公司Mentor Graphic占有国内78%的市场份额,海外EDA软件企业占有国内至少86%的市场份额。在IP核领域,ARM、Synopsys与Cadence占有全球66%的市场份额,国内龙头芯原股份在全球市占率为2%。

目前,国内EDA软件与IP核相关上市公司分别有华大九天、概伦电子与芯原股份,三家公司均于2021年在科创板上市。

公司简称 | 股票代码 | 主营业务 | 类别 |

华大九天 | A21150.SH | 公司主要产品包括模拟电路设计全流程EDA工具系统、数字电路设计EDA工具、平板显示电路设计全流程EDA工具系统和晶圆制造EDA工具等EDA工具软件产品。 | EDA软件:模拟电路设计全流程EDA软件、数字电路设计EDA软件、平板显示电路设计全流程EDA软件。晶圆制造EDA工具 |

概伦电子 | 688206.SH | 公司主要产品及服务包括制造类EDA工具、设计类EDA工具、半导体器件特性测试仪器和半导体工程服务等, | EDA软件:设计和制造类EDA软件 |

芯原股份 | 688521.SH | 公司是一家依托自主半导体IP,为客户提供平台化、全方位、一站式芯片定制服务和半导体IP授权服务的企业。 | IP核 |

三、芯片设计行业主要上市公司财务概览

国内EDA与IP核领域企业的发展面临较大困难,除缺乏资金与人才外更缺乏下游产业的支持。芯片设计的每一环节高度关联,海外三巨头经过长时间发展已形成覆盖面完整的工具链条,使下游厂商对其具有极大的黏性。国内企业目前仅能提供部分领域产品,获得客户较难,因而更难获得足够的下游数据改良迭代自身产品,与三巨头的差距不断增大。国内半导体IP巨头芯原股份依旧处于亏损状态。

公司简称 | 2021年上半年营业收入(亿元) | 2021年上半年毛利率 | 动态市盈率(2022年1月11日) |

华大九天 | 1.82 | 88.46%(全产品) | / |

概伦电子 | 0.54 | 100% | 717.16 |

芯原股份 | 2.14 | 96.69% | 亏损 |

四、芯片设计行业主要上市公司近期动态

公司简称 | 2021年动向 |

华大九天 | 已过会,预计募资25.51亿元,其中5亿元用于电路仿真及数字分析优化EDA工具升级项目;2.9亿元用于模拟设计及验证EDA工具升级项目;4.3亿元用于面向特定类型芯片设计的EDA工具开发项目;5.6亿元用于数字设计综合及验证EDA工具开发项目 |

概伦电子 | 公司成功上市募资12.09亿元,其中3.8亿元用于建模及仿真系统升级建设项目;3.4亿元用于设计工艺协同优化;2.5亿元用于建设研发中心;1.5亿元用于投资并购;剩余补充流动资金 |

芯原股份 | 公司开发的基于高性能总线架构和FLC终极内存/缓存技术的可复用的ASIC软硬件平台在2021年上半年完成流片。 |